功率MOS管失效损坏电气过应力失效特征

当功率MOSFET失效时,通常会造成广泛的损害。本文提供了常见电气过应力故障模式下的故障特征目录。该文章可用于对故障的根本原因进行调查,以改善模块设计和可靠性。

功率MOSFET在最小化自身内部功耗情况下,常被用来高电压和大电流开关。然而在一些故障的条件下,承载的电压,电流和功率是有可能超过MOSFET的能力的。错误条件既可能由电路失效导致的,也有可能由像电机堵转一样的机械问题导致的。这就导致了电气过应力(EOS)。EOS典型的失效结果就是MOSFET中至少两个甚至三个管脚短路(漏极,源极,栅极)。另外从MOSFET烧毁的痕迹,晶圆的裂痕或是极限情况下塑料包装的损毁,都证明了MOSFET自身的高功率会导致器件的损坏。

检查烧痕的大小和位置(故障识别标志)提供了有关导致故障的故障条件类型的信息,常见故障条件为:

- 静电放电(ESD)

- 电压失效(UIS)-通常称为雪崩或耐久性

- SOA失效(过电流)

- 发热损坏

1.电压失效(UIS)-通常称为雪崩或耐久性

MOSFET漏极-源极间的电压超过器件额定V_{DSS}电压值到达击穿电压V_{(BR)DSS}(根据击穿电流其值不同)并超出一定的能量限度而导致的一种常见的失效模式。雪崩失效Unclamped Inductive Switching(UIS)分为单次雪崩和重复雪崩。

– 单次雪崩事件就是器件在应用中由于错误的条件导致出现雪崩事件,例如电器过载。电路应用中是没有预先为这类雪崩做预防设计的。

– 重复雪崩是指电路应用中雪崩式MOSFET的预期工作模式。这里说的雪崩式设计的性能,而且不依赖于雪崩事件发生的次数。

器件要想安全地工作在雪崩模式下,必须要满足下面的两个条件:

1. I_{DS(AL)S}不能超过重复雪崩安全工作区域曲线。

2. T_{j(av)}不能超过器件最高限制温度。

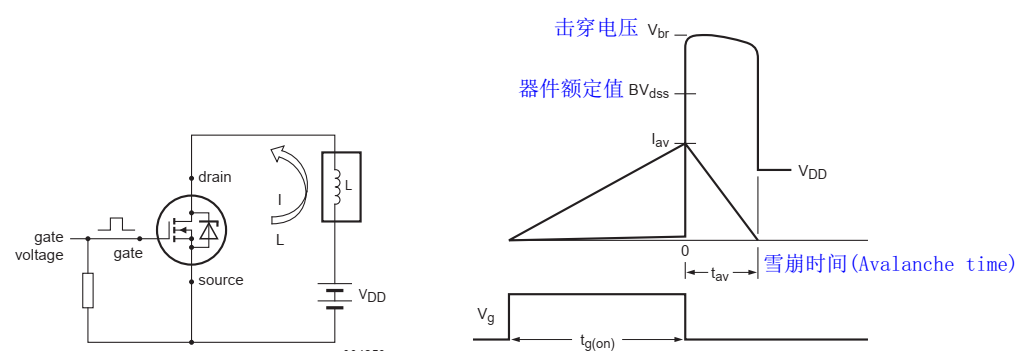

单次雪崩

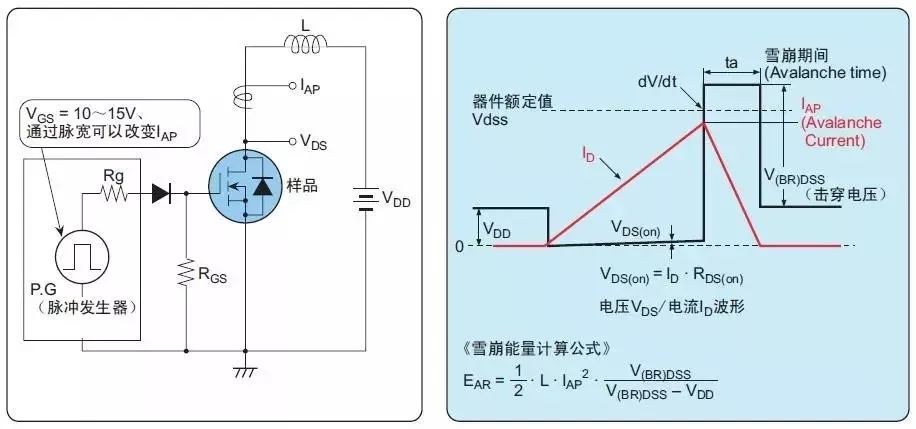

如下图,在栅极提供一个电压脉冲来导通MOSFET,负载电流根据电感量L和漏极电压V_{dd},开始爬升。在栅极电压脉冲结束的时候,MOSFET被迫关闭。电感中的电流继续流过,这就引起MOSFET两端的电压迅速上升。这个过电压被钳在了击穿电压V_{BR},一直持续到电流下降到0,正如下图中展示的那样。

通常,V_{BR}是:V_{BR}\approx1.3 \times V_{(BR)DSS}

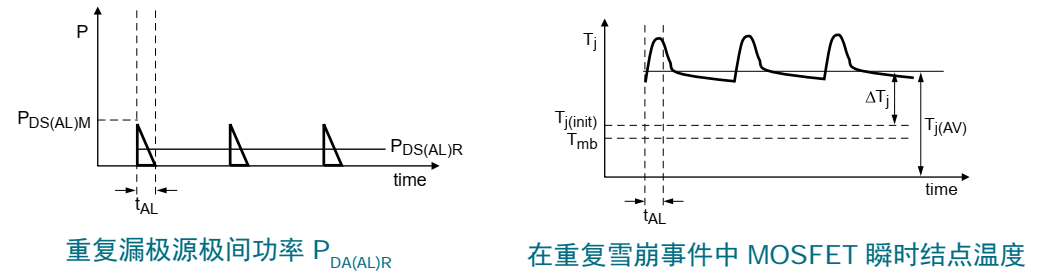

图2-1:UIS 耐久性测试的电路和 UIS 电路中获得的波形

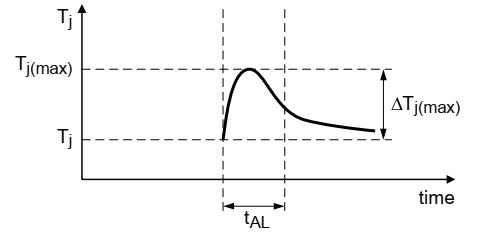

MOSFET的单次雪崩事件的失效机理是由于结点温度超过了最大温度限值,持续的时间一般在微秒量级。在这种情况下,MOSFET会产生灾难性的损坏。如下图中,如由雪崩事件导致的瞬时温度超过了推荐的限值,热量不足以传递到芯片引线框和封装体,器件的风险增高。为了达到最佳的稳定性,这里的限值是由最大温度降额而来。

图:在一次雪崩事件期间 MOSFET 的瞬时结点温度曲线

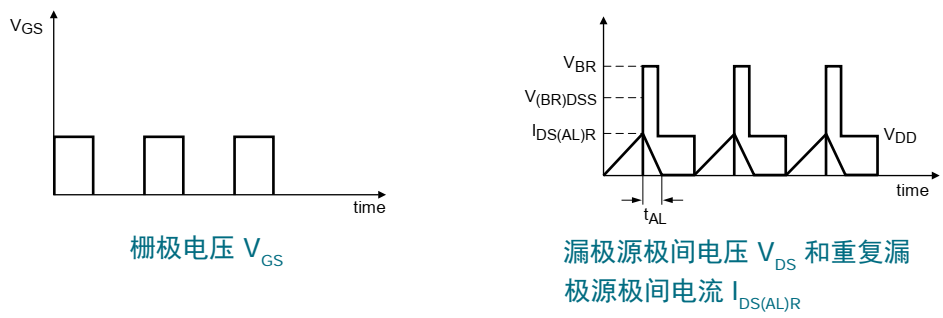

重复雪崩

正如之前讨论过的,重复雪崩是指工作中包含重复单次雪崩事件。直到近年来,大多数厂商都避免提供与功率MOSFET重复雪崩能力有关的数据。这主要是由于这种工作情况的复杂性和以及识别此种工况下元器件物理衰减过程的难度而决定的。

由于雪崩事件具有创伤的性质,重复雪崩工作可能会是对MOSFET有害的。即使出现了一个低于单次UIS限值的个别雪崩事件也是有害的。这种工作引入了额外的参数,如频率,占空比和雪崩事件中的热阻抗。然而降低单次限值来定义多次重复雪崩的SOAR是可以实现的。

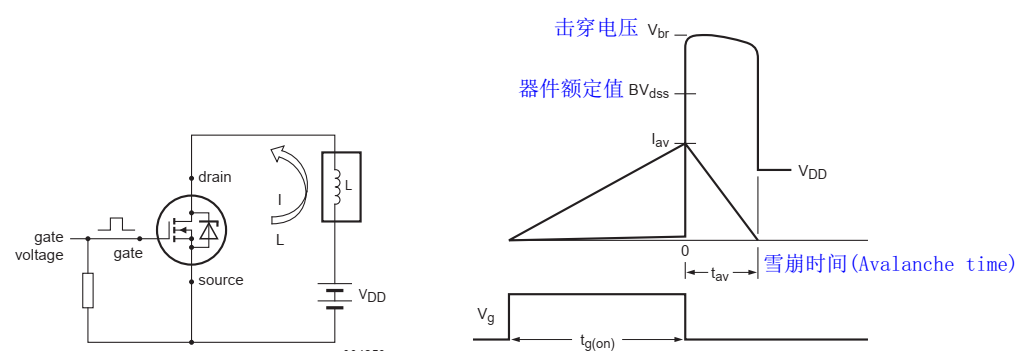

图2-1中展示了重复的UIS工作的测试电路。提供给栅极的频率和占空比的一串电压脉冲。导致器件的击穿电压V_{BR}。和流过负载的漏极电流I_{D}和单次UIS是一样的。此时的I_{D}是由漏极和源极的重复雪崩电流I_{DS(AL)S}决定的,详见下图。

通过广泛地研究,清楚地发现当雪崩发生时不止存在一种失效或是损坏模式。对于重复雪崩工作,温度并不是唯一的限制因素。然而,通过限定温度和重复的雪崩电流,可以定义出安全的使用环境,使得器件不会出现退化。这样的话也就相当于允许器件在重复UIS条件下工作。

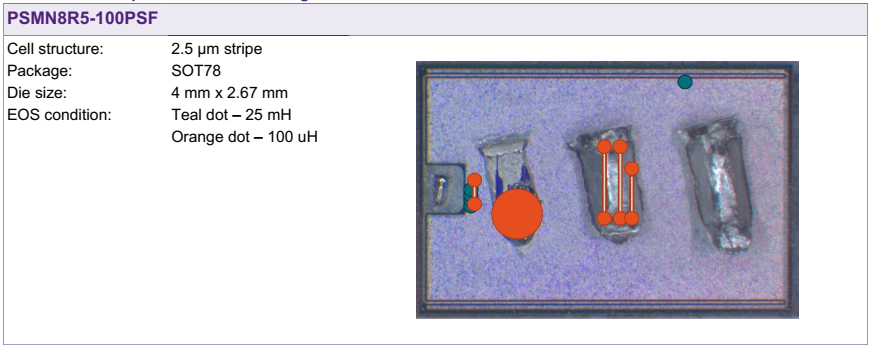

故障特征模拟

用一个标准的UIS电路来提供感性能量的脉冲;详见AEC-0101-004-REV-May 1.5,1996。选一个固定的电感值。在关闭MOSFET之前电感中的电流要逐渐的增加,直到器件失效。

UIS模拟的是当电路中存在一个电感,并当MOSFET关闭时的情况。电感量可以是任意的(就像柴油机系统中的喷油线圈)或是寄生的。因为电感中的电流并不能瞬间衰减到0,MOSFET的漏极源极电压上升,器件就会进入雪崩击穿,之前存储在电感中的能量就会通过MOSFET释放。

图2:UIS 耐久性测试的电路和 UIS 电路中获得的波形

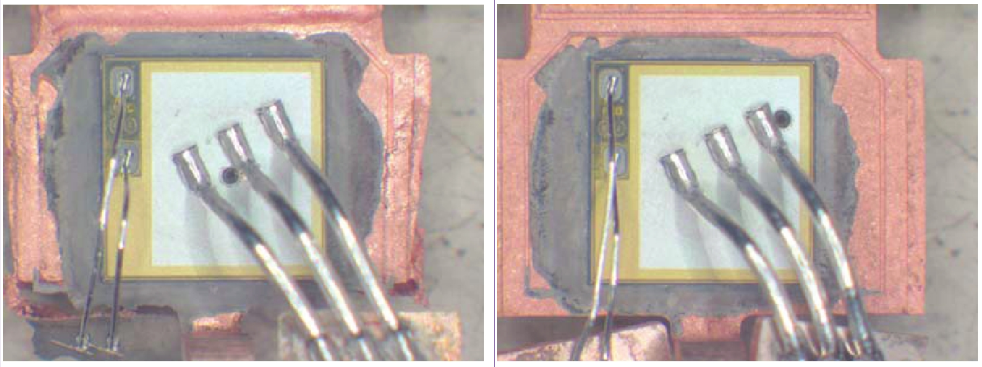

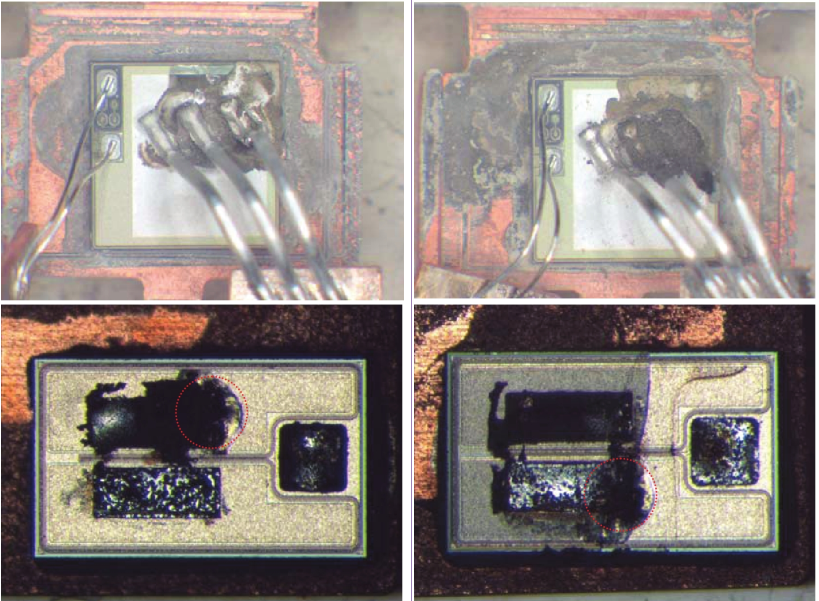

失效点可以在一个MOSFET基础单元中找到。烧毁的痕迹在外形上通常是圆的,这表示一个失效点中心位置以及随后发生了热损坏。

如果雪崩事件的持续时间为ms级别的,就会在流过最大电流的晶圆中间的位置呈现出烧过的痕迹。因为连接引线和晶圆结合的位置的电流密度较高,所以失效的位置经常出现在这里。但是因为有散热片的存在,所以往往并不会在连接引线的结点的正下方出现失效,而是发生在晶圆最热的地方。

对于us级的短暂的雪崩事件,烧毁的痕迹可能发生在整个晶圆的任意地方。这种情况下不太可能电流汇集在一起或者在这个事件段内器件给自己加热,所以器件内部的温升是比较均匀的。即使对于更短的雪崩事件,由于边缘地方的单元是不连续的,烧毁可能会发生在晶圆的转角处。

2.发热损坏

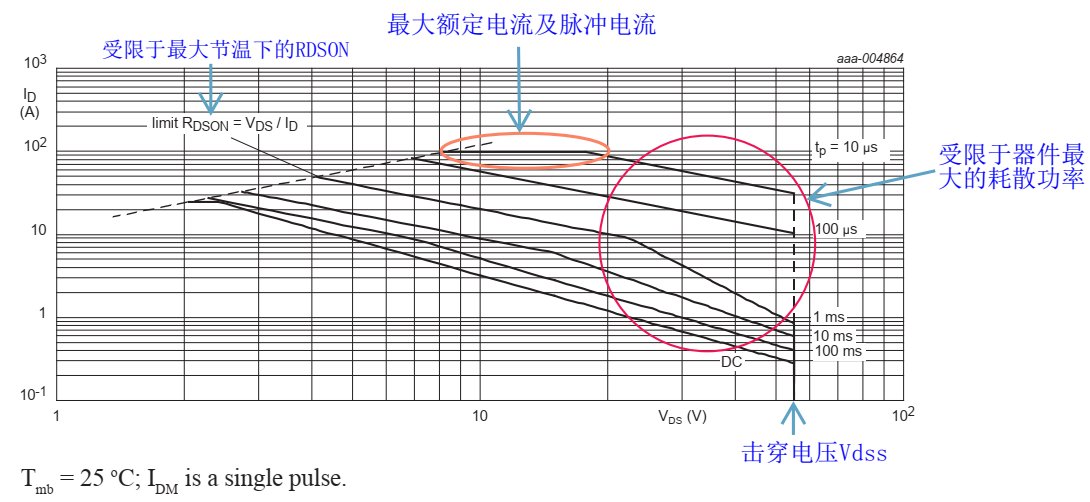

所有MOSFET的数据手册中都会包含安全工作区域的图表。工作在安全区域以外,MOSFET中的功率来不及耗散,就会导致产生的热量超出了器件的能力,最终导致器件失效。

图:安全工作区域(SAO); 漏极的连续电流和峰值电流和漏极源极电压的关系

热失效通常发生在器件开关或是钳位的感性负载应用中。除非超出了SOA安全工作区域,这本身并不是一个错误的工作状态。线性模式EOS模拟的是当一个MOSFET工作在线性模式很长时间的情况。这种情况也有可能发生在当试图导通MOSFET,而栅极的驱动电压又过低的时候。还有可能出现在施加较高的漏极电压,并试图维持住MOSFET关闭的时候。如果栅极的连接断开,栅极电压的容性会上升,也有可能出现线性模式的失效。

故障特征模拟

给MOSFET提供固定的漏极源极电压,并提供特定时长的脉冲电流,逐步地升高电流值,直到MOSFET出现失效为止。

晶圆的最热点就会是失效的位置,通常会出现在晶圆中间的部位。晶圆的中间位置往往是流过最大电流,且散热能力下降的地方。失效的位置也会出现在连接线和晶圆结合的位置,因为这里的电流密度最高,但由于有散热片的原因,失效往往不会出现在结点的正下方。

3.SOA失效(过电流)

功率MOSFET的数据手册中都回列出能够承载的最大电流值。这个值取决于连接引线和夹片在熔断之前承载电流的能力,超过这个限值器件就会导致致命的失效。

如果在电路中没有能够限制电流的器件,当MOSFET导通时就会出现过电流的情况,导致供电电压完全加在了MOSFET的漏极源极端子上。一般会发生在负载短路时。也有可能发生在半桥的配置中,如果上下MOSFET同时导通随后发生过电流。

故障特征

失效位置起初发生在承载电流的引线或夹片与晶圆连接的地方。通常来说这种损坏是很多的,但是当过电流时,会看到金属和焊接点溶化后的痕迹散布在整个晶圆的表面。

对于打隐线的封装,经常会出现引线融化。对于clip-bonded的封装,通常会观察到晶圆出现裂痕。

4.ESD失效(静电放电失效)

ESD失效分为 机械产生的ESD 或者 人体产生的ESD

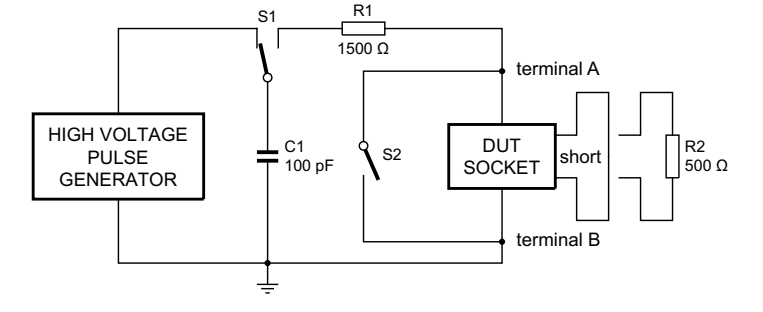

- 人体模式的ESD模拟了一个超过了栅极源极或栅极漏极之间的氧化物所能承受的最大电压的尖峰电压施加到MOSFET上。在电压源和MOSFET之间有一个1500Q的串联电阻,它可以限制MOSFET栅极电压的上升速率。无论是人体接触,电气测试设备或是多功能的电路都能很容易地提供这样的电压脉冲。

-

机械模式的ESD略不同于人体模式的ESD,在电压源和MOSFET之间会有一个最小的串联电阻,这就会导致MOSFET的栅极电压迅速上升。而人体上有一个1500Q的串联电阻限制了上升速率。

故障条件模拟

ESD 电压脉冲模拟标准的人体模式ESD电路;详见AEC-Q101-REV-May 15,1996。逐步地提升施加的电压,直到器件发生失效为止。

图:人体模型ESD模拟仿真的典型电路

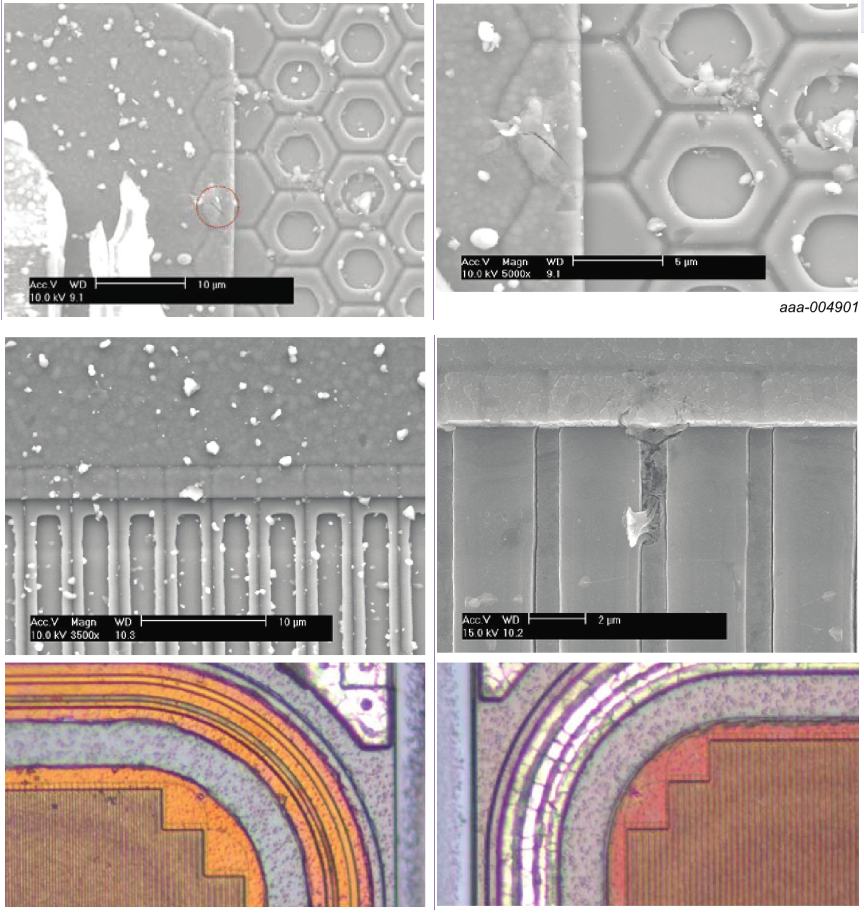

失效通常发生在MOSFET结构的边缘位置的单元中。外侧边缘的单元和靠近栅极的单元是最先受到电压脉冲的冲击的,这里也是电压超过栅极氧化物能力的第一个地方。由于栅极电压缓慢地上升,失效位置并不会表现出非常明显的有靠近栅极的趋势,在这一点上人体模式和机械模式是不同的。

图:人体模式 ESD 失效特征的案列

个人见解如果有什么错误欢迎指正!